ASIC development at MPG HLL

With the increasing degree of complexity of our detectors, we also have to provide the necessary readout electronics for the construction of the complete detector systems. For this reason, a joint developer group for application-specific integrated circuits (ASIC) with specialists who cover all relevant areas of the electronics development process was formed by the two Max Planck Institutes involved, the MPI for Physics and the MPI for Extraterrestrial Physics From the different areas of application of the detectors in the participating institutes, we can use the synergy effects for the common parts of the developed ASIC's and share the necessary infrastructure for the development process. This joint development group also shares the development work in the test and qualification processes for the ASIC's and the detector systems through a common test strategy and platform.

Why do we have to develop our own ASICs?

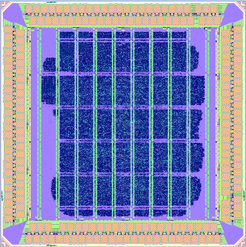

64x64 DEPFET macropixel matrix with two 64 channel

ASTEROID ASIC's for the Bepi X-Ray experiment

Due to the nature of the requirements for the readout electronics for our detector systems, such as very low noise or very high processing speed, we can usually not use commercially available circuits to set up the necessary signal processing chain. to build. We therefore have to develop special solutions for the challenges in the areas of radiation hardness, total power consumption, readout speed and low-noise readout. We also need special circuits for the testing and further development of our detector structures, for which the same requirements do not apply as for the final application electronics to support the debugging of new detector concepts and implementations. Furthermore, we can benefit from the joint development of the detector structures and the associated readout electronics in our laboratory to optimize the overall performance of the resulting systems.

What kind of developments are we doing?

We can according to the requirements of the projects the whole area of , ASIC development from the pure analog input stage via so-called mixed signal Readout circuits for purely digital data processing cover units.

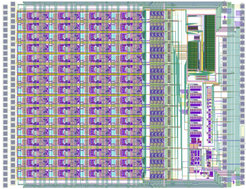

64 channel version of the ASTEROID ASIC for source follower

DEPFET read out for fast, low noise applications

Design examples:

The ASIC family ASTEROID / VERITAS

Starting with a 4 channel version of a multiplexed DEPFET source follower readout circuit carries this ASIC Family in a 0.35µm Austria Microsystems (AMS) Mixed Signal technology the use of a radiation hard register and memory architecture. The modular circuit concept behind this ASIC's allows the development of derived ones Variants with different input levels for CCD and DEPFET sensors and number of channels.